Слайд 1Системное программное обеспечение

Лекция № 2 «Регистровая память»

Слайд 2Регистровая память

Регистровая память Intel процессоров, начиная с 80486 и Pentium, содержит 32 регистра в той или иной мере доступных для использования программистом. Данные регистры можно разделить на две большие группы: 16 пользовательских регистров 16 системных регистров Как следует из названия, пользовательскими регистры называются потому, что программист может использовать их при написании своих программ.

Слайд 3

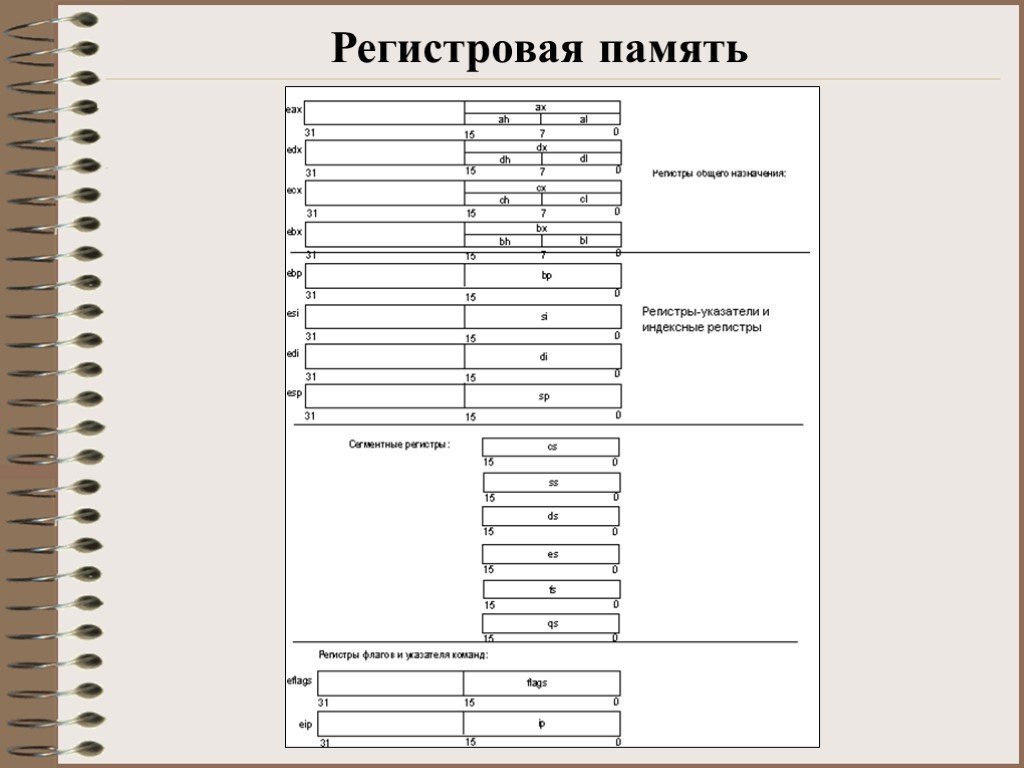

Слайд 4Так как регистры общего назначения, регистры–указатели и индексные регистры физически находятся в микропроцессоре внутри арифметико–логического устройства (АЛУ), то их еще называют регистрами АЛУ: eax/ax/ah/al (Accumulator register) — аккумулятор. Применяется для хранения промежуточных данных ebx/bx/bh/bl (Base register) — базовый регистр. Применяется для хранения базового адреса некоторого объекта в памяти ecx/cx/ch/cl (Count register) — регистр–счетчик. Применяется в командах, производящих некоторые повторяющиеся действия edx/dx/dh/dl (Data register) — регистр данных. Часто используется для передачи данных в подпрограммы

Слайд 5esi/si (Source Index register) — индекс источника. Этот регистр в операциях со строками содержит текущий адрес элемента в строке–источнике edi/di (Destination Index register) — индекс приемника (получателя). Этот регистр в операциях со строками содержит текущий адрес в строке–приемнике esp/sp (Stack Pointer register) — регистр указателя стека. Содержит указатель вершины стека в текущем сегменте стека ebp/bp (Base Pointer register) — регистр базового указателя в стеке. Предназначен для организации произвольного доступа к данным внутри стека

Слайд 6Большинство регистров могут использоваться при программировании для хранения операндов практически в любых сочетаниях. Отмеченное функциональное назначение отражает лишь наиболее частую область применения. Сегментные регистры В программной модели микропроцессора имеется шесть сегментных регистров: cs, ss, ds, es, gs, fs. Их существование обусловлено спецификой организации и использования оперативной памяти микропроцессорами Intel. Она заключается в том, что микропроцессор аппаратно поддерживает структурную организацию программы в виде трех частей, называемых сегментами (кода, данных и стека). Соответственно, такая организация памяти называется сегментной.

Слайд 7Для того чтобы указать на сегменты, к которым программа имеет доступ в конкретный момент времени, и предназначены сегментные регистры. Фактически в этих регистрах содержатся адреса памяти, с которых начинаются соответствующие сегменты: Сегмент кода. Содержит команды программы. Для доступа к этому сегменту служит регистр cs (code segment register) — сегментный регистр кода. Он содержит адрес сегмента с машинными командами, к которому имеет доступ микропроцессор (то есть эти команды загружаются в конвейер микропроцессора). Сегмент данных. Содержит обрабатываемые программой данные. Для доступа к этому сегменту служит регистр ds (data segment register) — сегментный регистр данных, который хранит адрес сегмента данных текущей программы.

Слайд 8Сегмент стека. Этот сегмент представляет собой область памяти, называемую стеком. Работу со стеком микропроцессор организует по следующему принципу: последний записанный в эту область элемент выбирается первым (дисциплина обслуживания LIFO – Last Input First Output). Для доступа к этому сегменту служит регистр ss (stack segment register) — сегментный регистр стека, содержащий адрес сегмента стека. Дополнительный сегмент данных. Если программе недостаточно одного сегмента данных, то она имеет возможность использовать еще три дополнительных сегмента данных. Адреса дополнительных сегментов данных должны содержаться в регистрах es, gs, fs (extension data segment registers).

Слайд 9Регистры флагов и указателя команд В микропроцессор включены несколько регистров, которые постоянно содержат информацию о состоянии как самого микропроцессора, так и программы, команды которой в данный момент загружены на конвейер. К этим регистрам относятся: регистр флагов eflags/flags регистр указателя команды eip/ip Используя эти регистры, можно получать информацию о результатах выполнения команд и влиять на состояние самого микропроцессора.

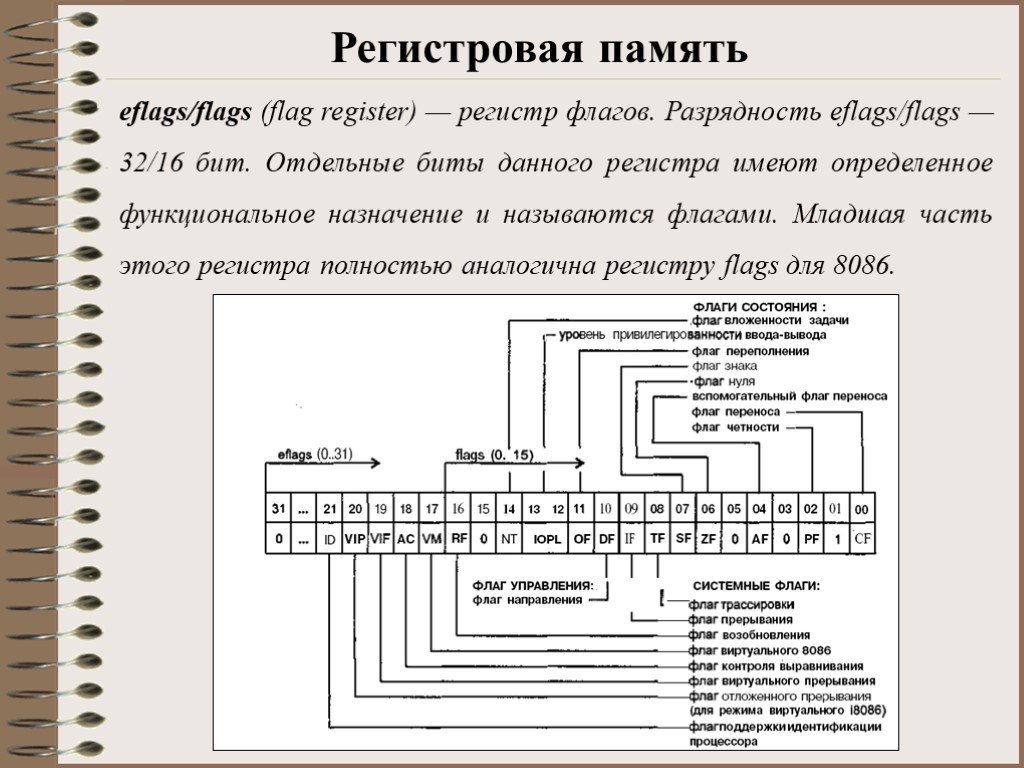

Слайд 10eflags/flags (flag register) — регистр флагов. Разрядность eflags/flags — 32/16 бит. Отдельные биты данного регистра имеют определенное функциональное назначение и называются флагами. Младшая часть этого регистра полностью аналогична регистру flags для 8086.

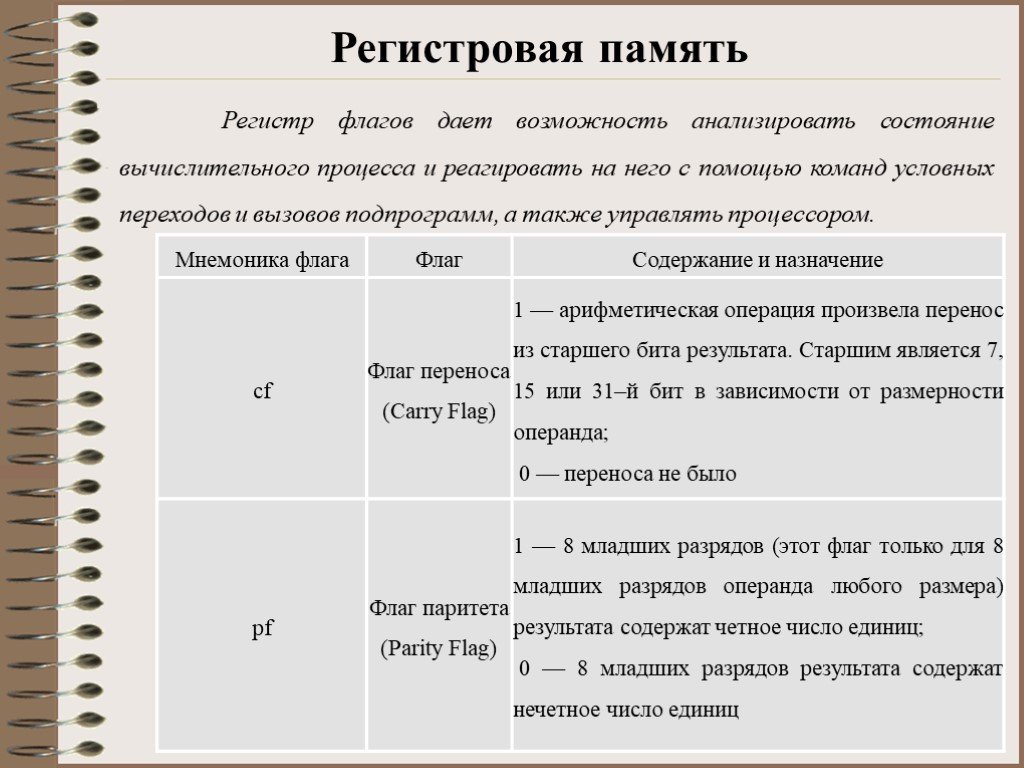

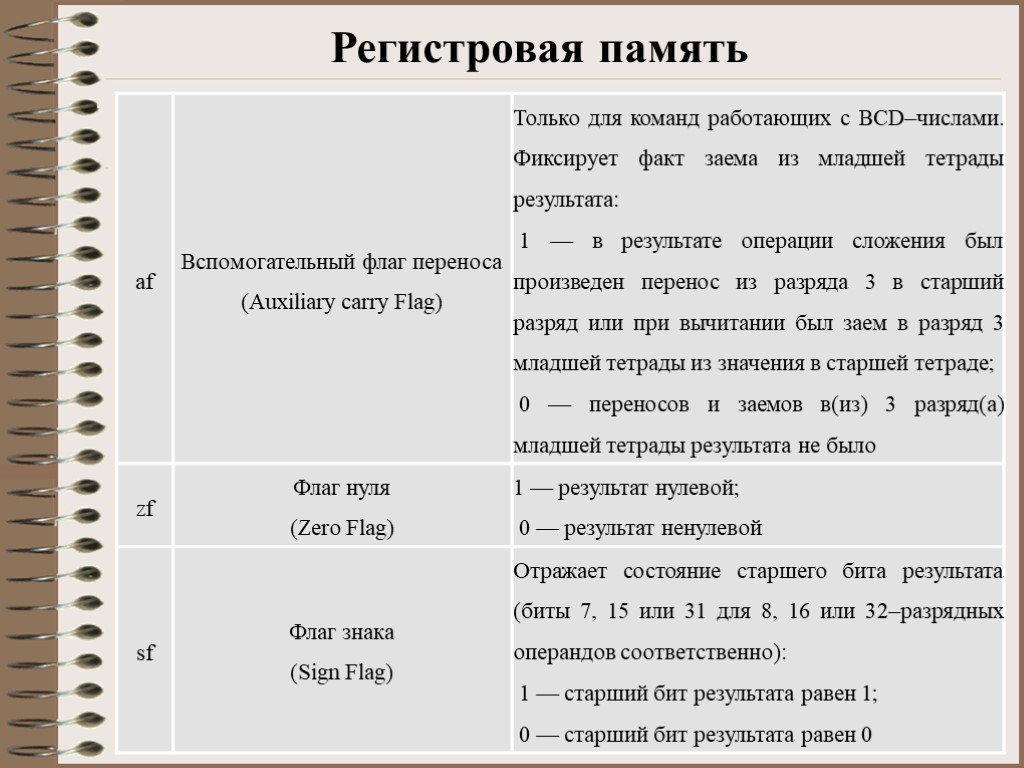

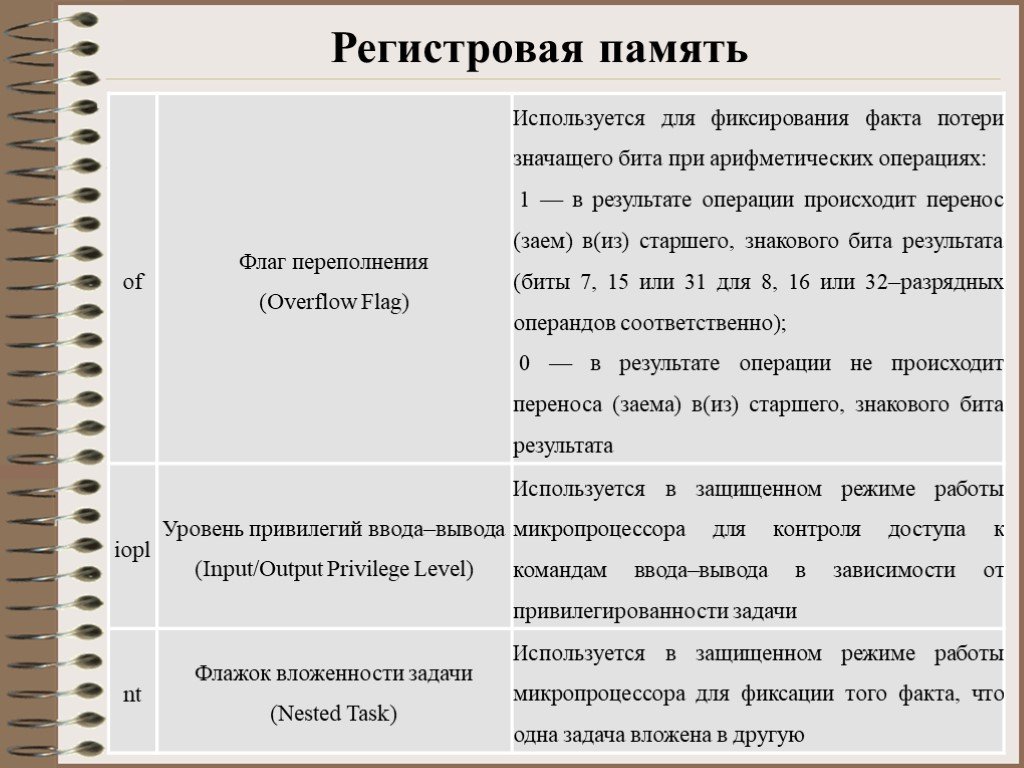

Слайд 11Регистр флагов дает возможность анализировать состояние вычислительного процесса и реагировать на него с помощью команд условных переходов и вызовов подпрограмм, а также управлять процессором.

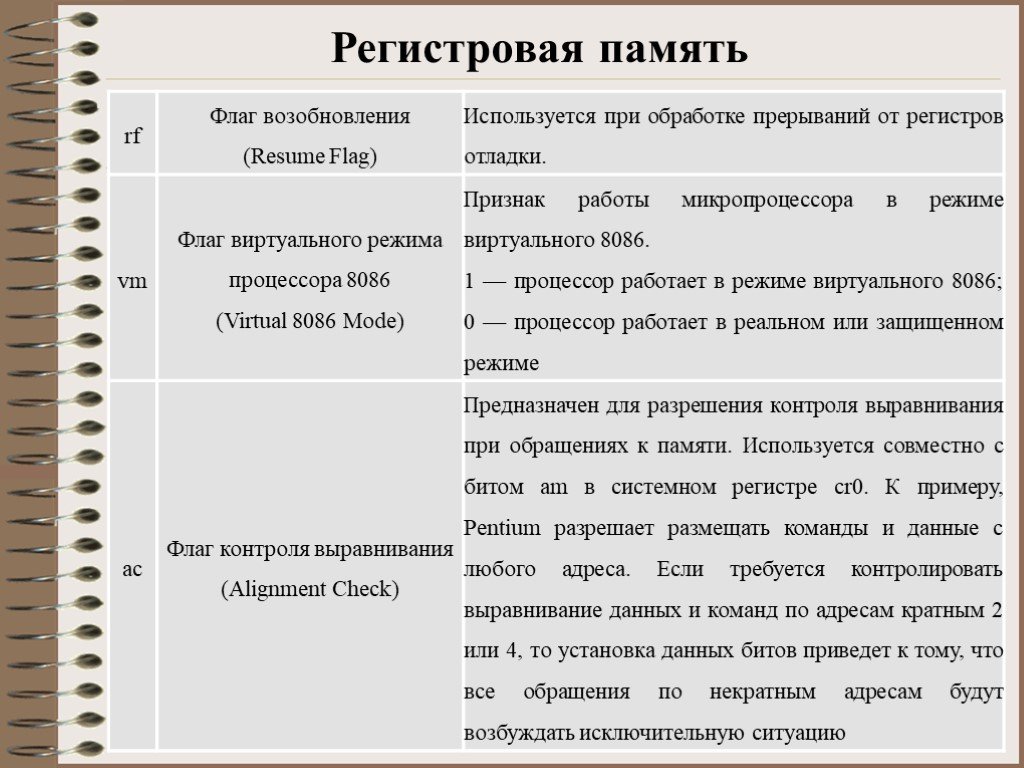

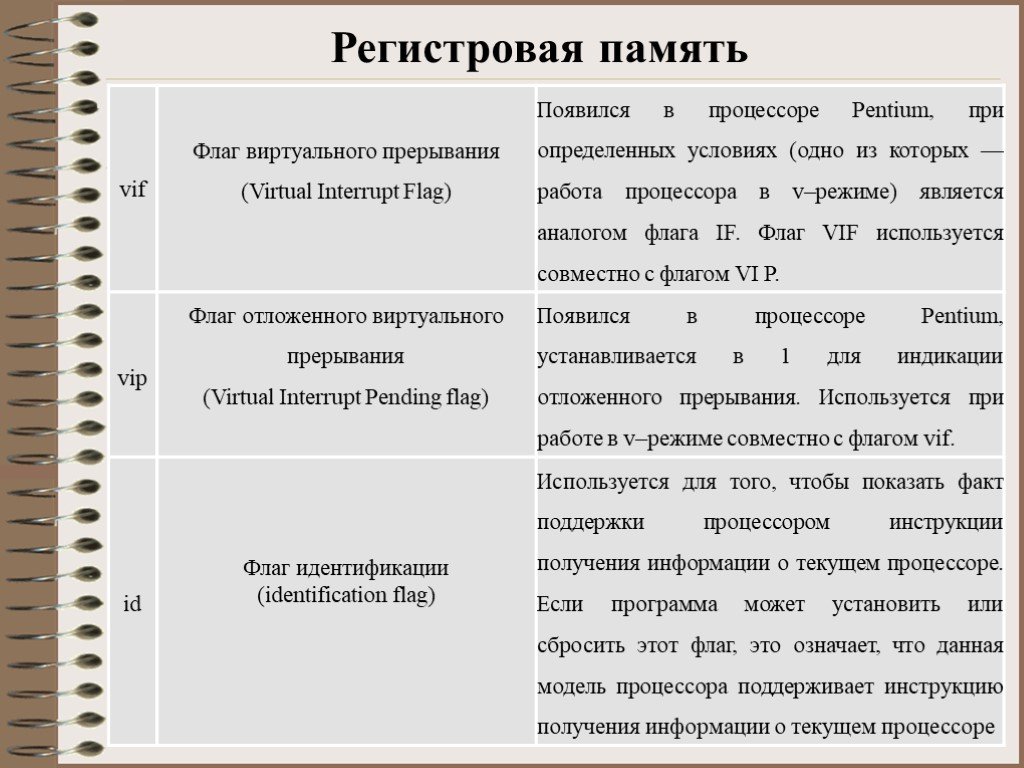

Слайд 12

Слайд 13

Слайд 14

Слайд 15

Слайд 16

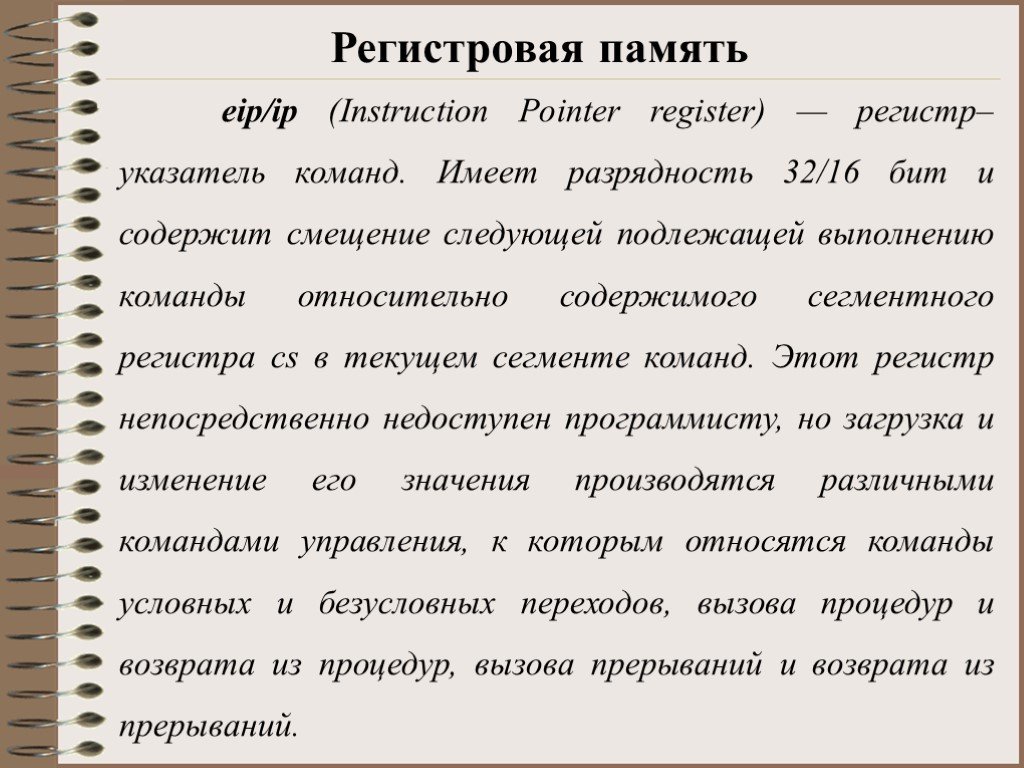

Слайд 17eip/ip (Instruction Pointer register) — регистр–указатель команд. Имеет разрядность 32/16 бит и содержит смещение следующей подлежащей выполнению команды относительно содержимого сегментного регистра cs в текущем сегменте команд. Этот регистр непосредственно недоступен программисту, но загрузка и изменение его значения производятся различными командами управления, к которым относятся команды условных и безусловных переходов, вызова процедур и возврата из процедур, вызова прерываний и возврата из прерываний.

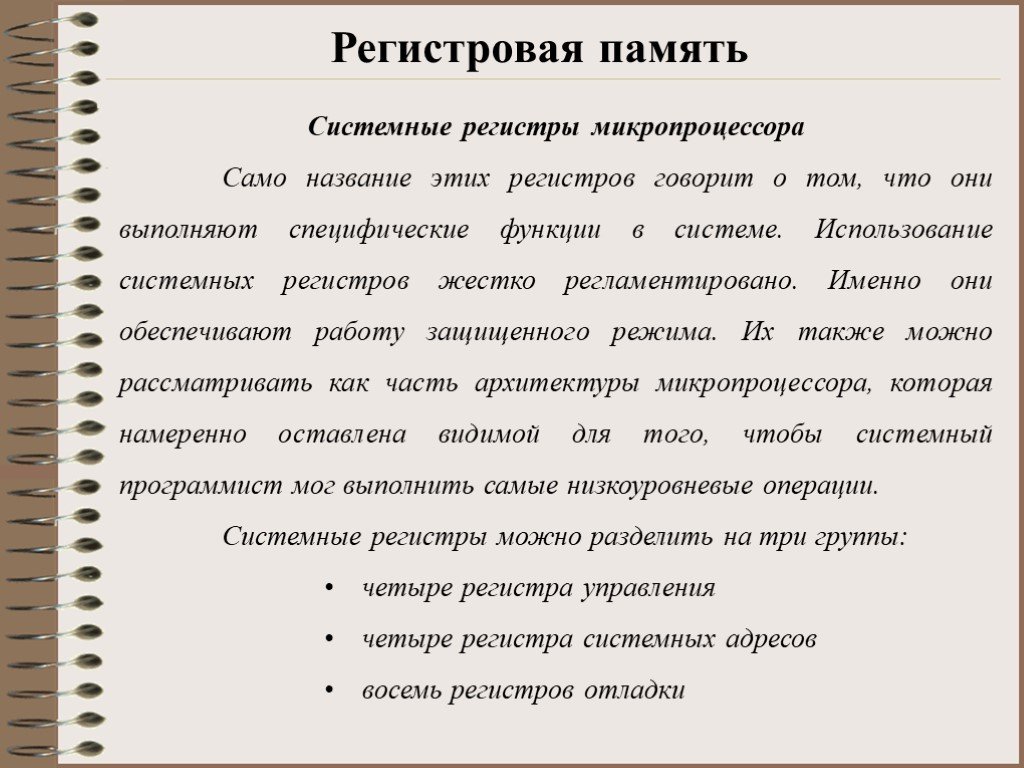

Слайд 18Системные регистры микропроцессора Само название этих регистров говорит о том, что они выполняют специфические функции в системе. Использование системных регистров жестко регламентировано. Именно они обеспечивают работу защищенного режима. Их также можно рассматривать как часть архитектуры микропроцессора, которая намеренно оставлена видимой для того, чтобы системный программист мог выполнить самые низкоуровневые операции. Системные регистры можно разделить на три группы: четыре регистра управления четыре регистра системных адресов восемь регистров отладки

Слайд 19Регистры управления В группу регистров управления входят 4 регистра: cr0, cr1, cr2, cr3. Эти регистры предназначены для общего управления системой. Регистры управления доступны только программам с уровнем привилегий 0. Хотя микропроцессор имеет четыре регистра управления, доступными являются только три из них — исключается cr1, функции которого пока не определены (он зарезервирован для будущего использования). Регистр cr0 содержит системные флаги, управляющие режимами работы микропроцессора и отражающие его состояние глобально, независимо от конкретных выполняющихся задач.

Слайд 20Назначение системных флагов: pe (Protect Enable), бит 0 — разрешение защищенного режима работы. Состояние флага показывает, в каком из режимов — реальном (pe=0) или защищенном (pe=1) — работает микропроцессор mp (Math Present), бит 1 — наличие сопроцессора. Всегда 1 ts (Task Switched), бит 3 — переключение задач. Процессор автоматически устанавливает этот бит при переключении на выполнение другой задачи am (Aligment Mask), бит 18 — маска выравнивания. Этот бит разрешает (am=1) или запрещает (am=0) контроль выравнивания cd (Cache Disable), бит 30, — запрещение кэш–памяти. С помощью этого бита можно запретить (cd=1) или разрешить (cd=0) использование внутренней кэш–памяти (кэш–памяти первого уровня) pg (PaGing), бит 31, — разрешение (pg=1) или запрещение (pg=0) страничного преобразования (использования страничной модели памяти)

Слайд 21Регистр cr2 используется при страничной организации памяти для регистрации ситуации, когда текущая команда обратилась по адресу, содержащемуся в странице памяти, отсутствующей в данный момент времени в оперативной памяти. В такой ситуации в процессоре возникает исключительная ситуация 14, и линейный 32–битный адрес команды, вызвавшей это исключение, записывается в регистр cr2. Имея эту информацию, обработчик исключения 14 определяет нужную страницу, осуществляет ее подкачку и возобновляет нормальную работу программы. Регистр cr3 (регистр каталога страниц первого уровня) используется при страничной организации памяти. Он содержит 20–битный физический базовый адрес каталога страниц текущей задачи. Этот каталог содержит 1024 32–битных дескриптора, каждый из которых содержит адрес таблицы страниц второго уровня. Каждая из таблиц страниц второго уровня содержит 1024 32–битных дескриптора, адресующих страничные кадры в памяти. Размер страничного кадра — 4 Кб.

Слайд 22Регистры системных адресов Эти регистры еще называют регистрами управления памятью. Они предназначены для защиты программ и данных в многозадачном режиме работы процессора. При работе в защищенном режиме процессора адресное пространство делится на: глобальное — общее для всех задач локальное — отдельное для каждой задачи Этим разделением и объясняется присутствие в архитектуре процессора следующих системных регистров: регистра таблицы глобальных дескрипторов gdtr (Global Descriptor Table Register), имеющего размер 48 бит и содержащего 32–битовый (биты 16—47) базовый адрес глобальной дескрипторной таблицы GDT и 16–битовое (биты 0—15) значение предела, представляющее собой размер в байтах таблицы GDT

Слайд 23регистра таблицы локальных дескрипторов ldtr (Local Descriptor Table Register), имеющего размер 16 бит и содержащего так называемый селектор дескриптора локальной дескрипторной таблицы LDT. Этот селектор является указателем в таблице GDT, который и описывает сегмент, содержащий локальную дескрипторную таблицу LDT регистра таблицы дескрипторов прерываний idtr (Interrupt Descriptor Table Register), имеющего размер 48 бит и содержащего 32–битовый (биты 16–47) базовый адрес дескрипторной таблицы прерываний IDT и 16–битовое (биты 0—15) значение предела, представляющее собой размер в байтах таблицы IDT

Слайд 2416–битового регистра задачи tr (Task Register), который содержит селектор, то есть указатель на дескриптор в таблице GDT. Этот дескриптор описывает текущий сегмент состояния задачи (TSS — Task Status Segment). Этот сегмент создается для каждой задачи в системе, имеет жестко регламентированную структуру и содержит контекст (текущее состояние) задачи. Основное назначение сегментов TSS — сохранять текущее состояние задачи в момент переключения на другую задачу Регистры отладки Группа регистров, предназначенных для аппаратной отладки. Средства аппаратной отладки впервые появились в микропроцессоре 80486. Аппаратно микропроцессор содержит восемь регистров отладки, но реально из них используются только 6.

Слайд 25Регистры dr0, dr1, dr2, dr3 имеют разрядность 32 бит и предназначены для задания линейных адресов четырех точек прерывания. Используемый при этом механизм следующий: любой формируемый текущей программой адрес сравнивается с адресами в регистрах dr0...dr3, и при совпадении генерируется исключение отладки с номером 1. Регистр dr6 называется регистром состояния отладки. Биты этого регистра устанавливаются в соответствии с причинами, которые вызвали возникновение последнего исключения с номером 1. Биты dr6 и их назначение: b0 — если этот бит установлен в 1, то последнее исключение (прерывание) возникло в результате достижения контрольной точки, определенной в регистре dr0;

Слайд 26b1 — аналогично b0, но для контрольной точки в регистре dr1 b2 — аналогично b0, но для контрольной точки в регистре dr2 b3 — аналогично b0, но для контрольной точки в регистре dr3 bd (бит 13) — служит для защиты регистров отладки bs (бит 14) — устанавливается в 1, если исключение 1 было вызвано состоянием флага tf = 1 в регистре eflags bt (бит 15) устанавливается в 1, если исключение 1 было вызвано переключением на задачу с установленным битом ловушки в TSS t = 1 Все остальные биты в этом регистре заполняются нулями. Обработчик исключения 1 по содержимому dr6 должен определить причину, по которой произошло исключение, и выполнить необходимые действия.

Слайд 27Регистр dr7 называется регистром управления отладкой. В нем для каждого из четырех регистров контрольных точек отладки имеются поля, с помощью которых можно уточнить следующие условия, при которых следует сгенерировать прерывание: место регистрации контрольной точки — только в текущей задаче или в любой задаче. Эти биты занимают младшие восемь бит регистра dr7 (по два бита на каждую контрольную точку (фактически точку прерывания), задаваемую регистрами dr0, dr1, dr2, dr3 соответственно) Первый бит из каждой пары — это так называемое локальное разрешение; его установка говорит о том, что точка прерывания действует если она находится в пределах адресного пространства текущей задачи.

Слайд 28Второй бит в каждой паре определяет глобальное разрешение, которое говорит о том, что данная контрольная точка действует в пределах адресных пространств всех задач, находящихся в системе. тип доступа, по которому инициируется прерывание: только при выборке команды, при записи или при записи/чтении данных. Биты, определяющие подобную природу возникновения прерывания, локализуются в старшей части данного регистра Кроме рассмотренных регистров к группе пользовательских регистров можно добавить: регистры сопроцессора ST0, ST1, ST2, ST3, ST4, ST5, ST6, ST7, предназначенные для написания программ, использующих тип данных с плавающей точкой

Слайд 29целочисленные регистры MMX–расширения ММХО, MMXl, MMX2, ММХЗ, ММХ4, ММХ5, ММХб, ММХ7 регистры MMX–расширения с плавающей точкой XMMO, XMM1, ХММ2, ХММЗ, ХММ4,ХММ5,ХММб,ХММ7 а к группе системных регистров: регистры типов областей памяти MTRR используются для аппаратного управления кэшированием в целях назначения соответствующих свойств областям памяти машиннозависимые регистры MSR используются для управления процессором, контроля за его производительностью, получения информации об ошибках для более поздних моделей процессоров.